# DC-to-DC Converter Control Circuits

The MC34063A Series is a monolithic control circuit containing the primary functions required for DC-to-DC converters. These devices consist of an internal temperature compensated reference, comparator, controlled duty cycle oscillator with an active current limit circuit, driver and high current output switch. This series was specifically designed to be incorporated in Step–Down and Step–Up and Voltage–Inverting applications with a minimum number of external components. Refer to Application Notes AN920A/D and AN954/D for additional design information.

- Operation from 3.0 V to 40 V Input

- Low Standby Current

- Current Limiting

- Output Switch Current to 1.5 A

- Output Voltage Adjustable

- Frequency Operation to 100 kHz

- Precision 2% Reference

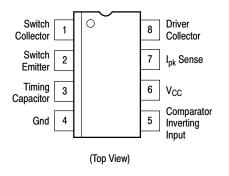

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.

#### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 11 of this data sheet.

#### **Representative Schematic Diagram**

This device contains 51 active transistors.

#### MAXIMUM RATINGS

| Rating                                                                                                                      | Symbol                                                 | Value                                 | Unit      |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------|-----------|

| Power Supply Voltage                                                                                                        | V <sub>CC</sub>                                        | 40                                    | Vdc       |

| Comparator Input Voltage Range                                                                                              | V <sub>IR</sub>                                        | -0.3 to +40                           | Vdc       |

| Switch Collector Voltage                                                                                                    | V <sub>C(switch)</sub>                                 | 40                                    | Vdc       |

| Switch Emitter Voltage (V <sub>Pin 1</sub> = 40 V)                                                                          | V <sub>E(switch)</sub>                                 | 40                                    | Vdc       |

| Switch Collector to Emitter Voltage                                                                                         | V <sub>CE(switch)</sub>                                | 40                                    | Vdc       |

| Driver Collector Voltage                                                                                                    | V <sub>C(driver)</sub>                                 | 40                                    | Vdc       |

| Driver Collector Current (Note 1.)                                                                                          | I <sub>C(driver)</sub>                                 | 100                                   | mA        |

| Switch Current                                                                                                              | I <sub>SW</sub>                                        | 1.5                                   | А         |

| Power Dissipation and Thermal Characteristics<br>Plastic Package, P, P1 Suffix<br>$T_A = 25^{\circ}C$<br>Thermal Resistance | PD                                                     | 1.25<br>100                           | W<br>°C/W |

| SOIC Package, D Suffix<br>$T_A = 25^{\circ}C$<br>Thermal Resistance                                                         | R <sub>θJA</sub><br>P <sub>D</sub><br>R <sub>θJA</sub> | 625<br>160                            | v<br>°C/W |

| Operating Junction Temperature                                                                                              | TJ                                                     | +150                                  | °C        |

| Operating Ambient Temperature Range<br>MC34063A<br>MC33063AV<br>MC33063A                                                    | T <sub>A</sub>                                         | 0 to +70<br>-40 to +125<br>-40 to +85 | °C        |

| Storage Temperature Range                                                                                                   | T <sub>stg</sub>                                       | -65 to +150                           | °C        |

Maximum package power dissipation limits must be observed.

ESD data available upon request.

| ELECTRICAL CHARACTERISTICS | $V_{CC} = 5.0 \text{ V}, \text{ T}_{A} = \text{T}_{low}$ to $\text{T}_{high}$ [Note 3.], unless otherwise specified. |

|----------------------------|----------------------------------------------------------------------------------------------------------------------|

|----------------------------|----------------------------------------------------------------------------------------------------------------------|

| Characteristics                                                                                                                                                              | Symbol                                | Min           | Тур        | Max           | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|------------|---------------|------|

| OSCILLATOR                                                                                                                                                                   | L                                     | •             |            | •             |      |

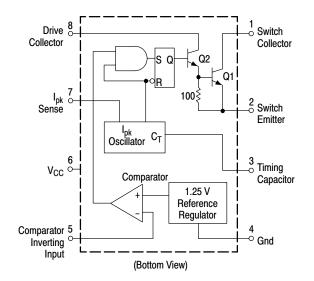

| Frequency (V <sub>Pin 5</sub> = 0 V, C <sub>T</sub> = 1.0 nF, T <sub>A</sub> = $25^{\circ}$ C)                                                                               | f <sub>osc</sub>                      | 24            | 33         | 42            | kHz  |

| Charge Current (V <sub>CC</sub> = 5.0 V to 40 V, T <sub>A</sub> = 25°C)                                                                                                      | I <sub>chg</sub>                      | 24            | 35         | 42            | μΑ   |

| Discharge Current (V <sub>CC</sub> = 5.0 V to 40 V, $T_A = 25^{\circ}C$ )                                                                                                    | I <sub>dischg</sub>                   | 140           | 220        | 260           | μA   |

| Discharge to Charge Current Ratio (Pin 7 to $V_{CC}$ , $T_A = 25^{\circ}C$ )                                                                                                 | I <sub>dischg</sub> /I <sub>chg</sub> | 5.2           | 6.5        | 7.5           | -    |

| Current Limit Sense Voltage ( $I_{chg} = I_{dischg}, T_A = 25^{\circ}C$ )                                                                                                    | V <sub>ipk(sense)</sub>               | 250           | 300        | 350           | mV   |

| OUTPUT SWITCH (Note 4.)                                                                                                                                                      |                                       |               |            |               |      |

| Saturation Voltage, Darlington Connection<br>(I <sub>SW</sub> = 1.0 A, Pins 1, 8 connected)                                                                                  | V <sub>CE(sat)</sub>                  | -             | 1.0        | 1.3           | V    |

| Saturation Voltage (Note 5.)<br>(I <sub>SW</sub> = 1.0 A, R <sub>Pin 8</sub> = 82 $\Omega$ to V <sub>CC</sub> , Forced $\beta \simeq 20$ )                                   | V <sub>CE(sat)</sub>                  | -             | 0.45       | 0.7           | V    |

| DC Current Gain (I <sub>SW</sub> = 1.0 A, V <sub>CE</sub> = 5.0 V, T <sub>A</sub> = 25°C)                                                                                    | h <sub>FE</sub>                       | 50            | 75         | _             | -    |

| Collector Off–State Current (V <sub>CE</sub> = 40 V)                                                                                                                         | I <sub>C(off)</sub>                   | -             | 0.01       | 100           | μΑ   |

| COMPARATOR                                                                                                                                                                   |                                       |               |            |               |      |

| Threshold Voltage<br>$T_A = 25^{\circ}C$<br>$T_A = T_{low}$ to $T_{high}$                                                                                                    | V <sub>th</sub>                       | 1.225<br>1.21 | 1.25<br>-  | 1.275<br>1.29 | V    |

| Threshold Voltage Line Regulation (V <sub>CC</sub> = 3.0 V to 40 V)<br>MC33063A, MC34063A<br>MC33363AV                                                                       | Reg <sub>line</sub>                   |               | 1.4<br>1.4 | 5.0<br>6.0    | mV   |

| Input Bias Current (V <sub>in</sub> = 0 V)                                                                                                                                   | I <sub>IB</sub>                       | -             | -20        | -400          | nA   |

| TOTAL DEVICE                                                                                                                                                                 | L                                     | •             | •          | •             | •    |

| Supply Current (V <sub>CC</sub> = 5.0 V to 40 V, C <sub>T</sub> = 1.0 nF, Pin 7 = V <sub>CC</sub> , V <sub>Pin 5</sub> > V <sub>th</sub> , Pin 2 = Gnd, remaining pins open) | I <sub>CC</sub>                       | _             | -          | 4.0           | mA   |

3.  $T_{low} = 0^{\circ}C$  for MC34063A, -40°C for MC33063A, AV  $T_{high} = +70^{\circ}C$  for MC34063A, +85°C for MC33063A, +125°C for MC33063AV

4. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient temperature as possible.

5. If the output switch is driven into hard saturation (non–Darlington configuration) at low switch currents (≤ 300 mA) and high driver currents (≥ 30 mA), it may take up to 2.0 µs for it to come out of saturation. This condition will shorten the off time at frequencies ≥ 30 kHz, and is magnified at high temperatures. This condition does not occur with a Darlington configuration, since the output switch cannot saturate. If a non–Darlington configuration is used, the following output drive condition is recommended:

Forced  $\beta$  of output switch :  $\frac{IC \text{ output}}{IC \text{ driver} - 7.0 \text{ mA}^*} \ge 10$

\* The 100  $\Omega$  resistor in the emitter of the driver device requires about 7.0 mA before the output switch conducts.

6. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient temperature as possible.

| Test                               | Conditions                                        | Results         |

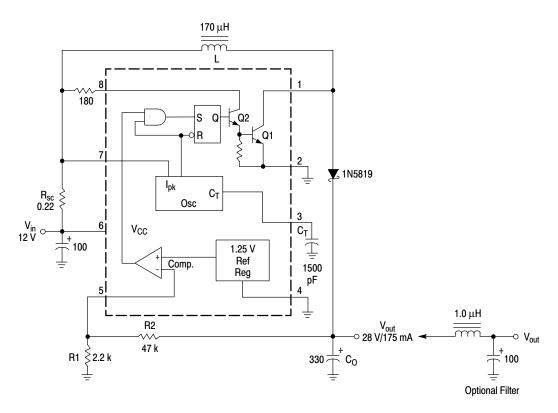

|------------------------------------|---------------------------------------------------|-----------------|

| Line Regulation                    | $V_{in}$ = 8.0 V to 16 V, $I_{O}$ = 175 mA        | 30 mV = ±0.05%  |

| Load Regulation                    | $V_{in}$ = 12 V, I <sub>O</sub> = 75 mA to 175 mA | 10 mV = ±0.017% |

| Output Ripple                      | V <sub>in</sub> = 12 V, I <sub>O</sub> = 175 mA   | 400 mVpp        |

| Efficiency                         | V <sub>in</sub> = 12 V, I <sub>O</sub> = 175 mA   | 87.7%           |

| Output Ripple With Optional Filter | V <sub>in</sub> = 12 V, I <sub>O</sub> = 175 mA   | 40 mVpp         |

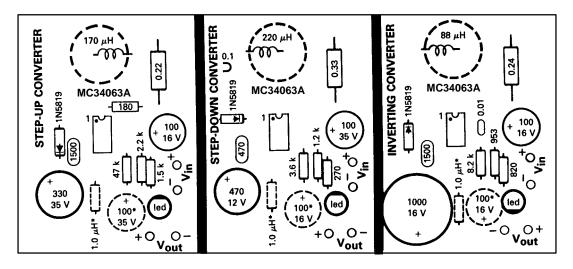

| Figure | 7. | Step-Up | Converter |

|--------|----|---------|-----------|

|--------|----|---------|-----------|

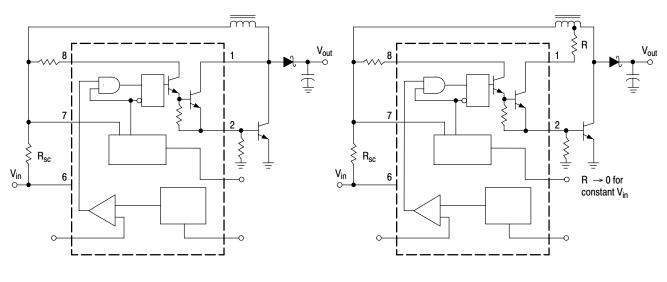

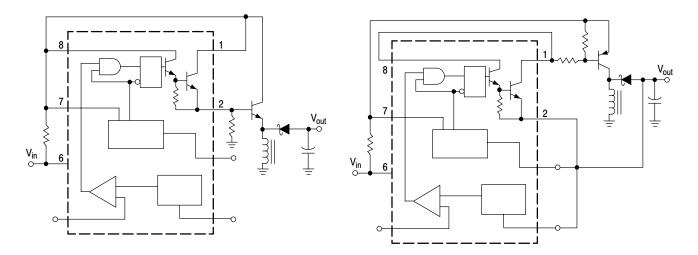

Figure 8. External Current Boost Connections for I<sub>C</sub> Peak Greater than 1.5 A

8a. External NPN Switch

8b. External NPN Saturated Switch

(See Note 7.)

7. If the output switch is driven into hard saturation (non–Darlington configuration) at low switch currents ( $\leq$  300 mA) and high driver currents ( $\geq$  30 mA), it may take up to 2.0 µs to come out of saturation. This condition will shorten the off time at frequencies  $\geq$  30 kHz, and is magnified at high temperatures. This condition does not occur with a Darlington configuration, since the output switch cannot saturate. If a non–Darlington configuration is used, the following output drive condition is recommended.

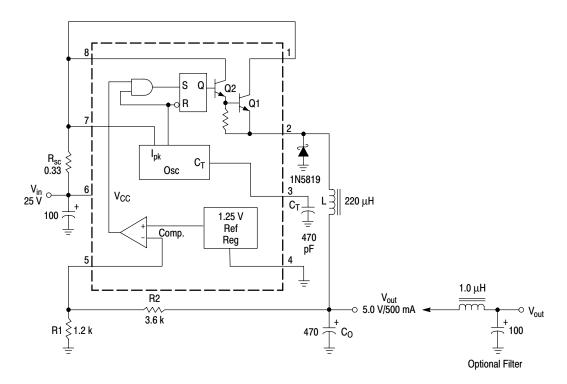

| Test                               | Conditions                                        | Results         |

|------------------------------------|---------------------------------------------------|-----------------|

| Line Regulation                    | $V_{in}$ = 15 V to 25 V, $I_O$ = 500 mA           | 12 mV = ±0.12%  |

| Load Regulation                    | $V_{in}$ = 25 V, I <sub>O</sub> = 50 mA to 500 mA | 3.0 mV = ±0.03% |

| Output Ripple                      | V <sub>in</sub> = 25 V, I <sub>O</sub> = 500 mA   | 120 mVpp        |

| Short Circuit Current              | $V_{in}$ = 25 V, R <sub>L</sub> = 0.1 $\Omega$    | 1.1 A           |

| Efficiency                         | V <sub>in</sub> = 25 V, I <sub>O</sub> = 500 mA   | 83.7%           |

| Output Ripple With Optional Filter | V <sub>in</sub> = 25 V, I <sub>O</sub> = 500 mA   | 40 mVpp         |

Figure 9. Step–Down Converter

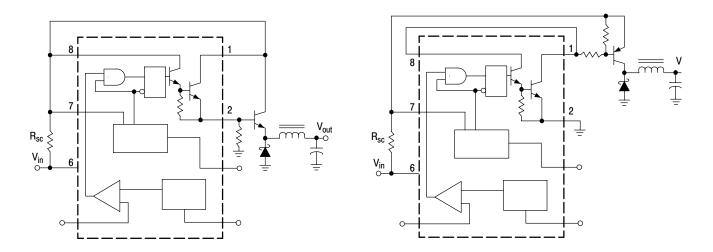

Figure 10. External Current Boost Connections for I<sub>C</sub> Peak Greater than 1.5 A

10a. External NPN Switch

10b. External PNP Saturated Switch

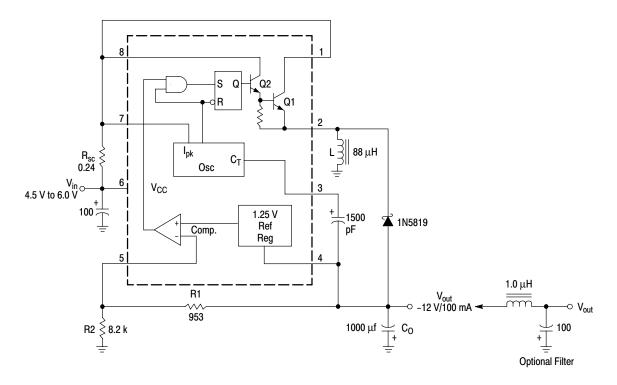

| Test                               | Conditions                                                       | Results          |

|------------------------------------|------------------------------------------------------------------|------------------|

| Line Regulation                    | $V_{in}$ = 4.5 V to 6.0 V, $I_O$ = 100 mA                        | 3.0 mV = ±0.012% |

| Load Regulation                    | $V_{in} = 5.0 \text{ V}, I_0 = 10 \text{ mA to } 100 \text{ mA}$ | 0.022 V = ±0.09% |

| Output Ripple                      | $V_{in} = 5.0 \text{ V}, I_0 = 100 \text{ mA}$                   | 500 mVpp         |

| Short Circuit Current              | $V_{in}$ = 5.0 V, R <sub>L</sub> = 0.1 $\Omega$                  | 910 mA           |

| Efficiency                         | $V_{in} = 5.0 \text{ V}, I_0 = 100 \text{ mA}$                   | 62.2%            |

| Output Ripple With Optional Filter | $V_{in} = 5.0 \text{ V}, I_0 = 100 \text{ mA}$                   | 70 mVpp          |

Figure 11. Voltage Inverting Converter

Figure 12. External Current Boost Connections for I<sub>C</sub> Peak Greater than 1.5 A12a. External NPN Switch12b. External PNP Saturated Switch

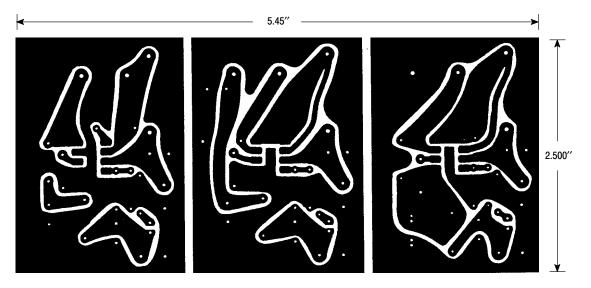

(Top view, copper foil as seen through the board from the component side)

(Top View, Component Side)

\*Optional Filter.

#### Figure 13. Printed Circuit Board and Component Layout (Circuits of Figures 7, 9, 11)

#### INDUCTOR DATA

| Converter         | Inductance (µH) | Turns/Wire          |

|-------------------|-----------------|---------------------|

| Step–Up           | 170             | 38 Turns of #22 AWG |

| Step-Down         | 220             | 48 Turns of #22 AWG |

| Voltage-Inverting | 88              | 28 Turns of #22 AWG |

All inductors are wound on Magnetics Inc. 55117 toroidal core.

| Calculation                           | Step–Up                                                                 | Step–Down                                                                           | Voltage-Inverting                                                          |

|---------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| t <sub>on</sub> /t <sub>off</sub>     | $\frac{V_{out}\ +\ V_{F}\ -\ V_{in(min)}}{V_{in(min)}\ -\ V_{sat}}$     | Vout <sup>+ V</sup> F<br>V <sub>in(min)</sub> <sup>- V</sup> sat <sup>- V</sup> out | $\frac{ V_out  \ + \ V_F}{ V_in  -  V_sat }$                               |

| (t <sub>on</sub> + t <sub>off</sub> ) | 1_f                                                                     | <u>1</u><br>f                                                                       | <u>1</u><br>f                                                              |

| t <sub>off</sub>                      | $\frac{\frac{t_{on} + t_{off}}{\frac{t_{on}}{t_{off}} + 1}$             | $\frac{\frac{t_{on} + t_{off}}{\frac{t_{on}}{t_{off}} + 1}$                         | $\frac{\frac{t_{on} + t_{off}}{t_{off}}}{\frac{t_{on}}{t_{off}} + 1}$      |

| t <sub>on</sub>                       | $(t_{on} + t_{off}) - t_{off}$                                          | $(t_{on} + t_{off}) - t_{off}$                                                      | $(t_{on} + t_{off}) - t_{off}$                                             |

| CT                                    | 4.0 x 10 <sup>-5</sup> t <sub>on</sub>                                  | 4.0 x 10 <sup>-5</sup> t <sub>on</sub>                                              | 4.0 x 10 <sup>-5</sup> t <sub>on</sub>                                     |

| I <sub>pk(switch)</sub>               | $2I_{out(max)}\left(\frac{t_{on}}{t_{off}} + 1\right)$                  | <sup>2I</sup> out(max)                                                              | $2I_{out(max)}\left(\frac{t_{on}}{t_{off}} + 1\right)$                     |

| R <sub>sc</sub>                       | 0.3/I <sub>pk(switch)</sub>                                             | 0.3/I <sub>pk(switch)</sub>                                                         | 0.3/I <sub>pk(switch)</sub>                                                |

| L <sub>(min)</sub>                    | $\left(rac{(V_{in(min)} - V_{sat})}{I_{pk(switch)}} ight)^t$ on(max)   | $\left(\frac{(V_{in(min)} - V_{sat} - V_{out})}{I_{pk(switch)}}\right)^{t} on(max)$ | $\left(\frac{(V_{in(min)} - V_{sat})}{I_{pk(switch)}}\right)^{t} con(max)$ |

| C <sub>O</sub>                        | 9 <mark>l<sub>out</sub>t<sub>on</sub><br/>V<sub>ripple(pp)</sub></mark> | $\frac{I_{pk(switch)}(t_{on} + t_{off})}{^{8V}ripple(pp)}$                          | 9 <del>I<sub>out</sub>ton</del><br>V <sub>ripple(pp)</sub>                 |

V<sub>sat</sub> = Saturation voltage of the output switch.

$V_F$  = Forward voltage drop of the output rectifier.

### The following power supply characteristics must be chosen:

V<sub>in</sub> – Nominal input voltage.

$\begin{array}{l} V_{in} - \text{Nominal input voltage.} \\ V_{out} - \text{Desired output voltage, } |V_{out}| = 1.25 \left(1 + \frac{R2}{R1}\right) \\ I_{out} - \text{Desired output current.} \\ f_{min} - \text{Minimum desired output switching frequency at the selected values of } V_{in} \text{ and } I_{O}. \end{array}$

Vripple(pp) - Desired peak-to-peak output ripple voltage. In practice, the calculated capacitor value will need to be increased due to its equivalent series resistance and board layout. The ripple voltage should be kept to a low value since it will directly affect the line and load regulation.

NOTE: For further information refer to Application Note AN920A/D and AN954/D.

#### Figure 14. Design Formula Table

#### **ORDERING INFORMATION**

| Device       | Package  | Shipping                 |

|--------------|----------|--------------------------|

| MC33063AD    | SO–8     | 98 Units / Rail          |

| MC33063ADR2  | SO–8     | 2500 Units / Tape & Reel |

| MC33063AP1   | DIP-8    | 50 Units / Rail          |

| MC33063AVD   | SO–8     | 98 Units / Rail          |

| MC33063AVDR2 | SO–8     | 2500 Units / Tape & Reel |

| MC33063AVP   | DIP-8    | 50 Units / Rail          |

| MC34063AD    | SO–8     | 98 Units / Rail          |

| MC34063ADR2  | SO–8     | 2500 Units / Tape & Reel |

| MC34063AP1   | DIP-8    | 50 Units / Rail          |

| MC34063BD    | SO–8     | 98 Units / Rail          |

| MC34063BDR2  | SO–8     | 2500 Units / Tape & Reel |

| MC34063AM    | SOEIAJ-8 | 94 Units / Rail          |

| MC34063AMEL  | SOEIAJ-8 | 1000 Units / Tape & Reel |

| MC34063AML1  | SOEIAJ-8 | 1000 Units / Tape & Reel |

| MC34063AML2  | SOEIAJ-8 | 2000 Units / Tape & Reel |

| MC34063AMR1  | SOEIAJ–8 | 1000 Units / Tape & Reel |

| MC34063AMR2  | SOEIAJ-8 | 2000 Units / Tape & Reel |

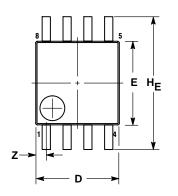

#### MARKING DIAGRAMS

| PDIP–8                                | PDIP–8                                            | SO-8                                     | SO-8                             | SOEIAJ–8                              |

|---------------------------------------|---------------------------------------------------|------------------------------------------|----------------------------------|---------------------------------------|

| P, P1 SUFFIX                          | P, P1 SUFFIX                                      | D SUFFIX                                 | D SUFFIX                         | M SUFFIX                              |

| CASE 626                              | CASE 626                                          | CASE 751                                 | CASE 751                         | CASE 968                              |

| 8 A A A A<br>3x063AP1<br>AWL<br>○YYWW | 8 A A A A<br>33063AVP<br>AWL<br>O YYWW<br>1 U U U | 8 A A A A<br>3x063<br>ALYWz<br>1 U U U U | 8月月日日<br>34063<br>○ALYWz<br>1日日日 | 8 R R R R<br>M063A<br>ALYW<br>1 U U U |

| х | = | 3 or 4      |

|---|---|-------------|

| z | = | A denotes A |

A denotes AD suffix

J denotes BD suffix

A = Assembly Location WL, L = Wafer Lot YY, Y = Year

WW, W = Work Week

#### PACKAGE DIMENSIONS

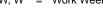

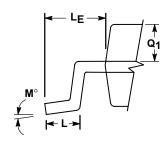

PDIP-8 P, P1 SUFFIX PLASTIC PACKAGE CASE 626-05 ISSUE K

NOTES:

- DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL

PACKAGE CONTOUR OPTIONAL (ROUND OR

- SQUARE CORNERS). DIMENSIONING AND TOLERANCING PER ANSI 3.

- Y14.5M, 1982.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 9.40        | 10.16 | 0.370     | 0.400 |

| В   | 6.10        | 6.60  | 0.240     | 0.260 |

| С   | 3.94        | 4.45  | 0.155     | 0.175 |

| D   | 0.38        | 0.51  | 0.015     | 0.020 |

| F   | 1.02        | 1.78  | 0.040     | 0.070 |

| G   | 2.54 BSC    |       | 0.100 BSC |       |

| Н   | 0.76        | 1.27  | 0.030     | 0.050 |

| J   | 0.20        | 0.30  | 0.008     | 0.012 |

| K   | 2.92        | 3.43  | 0.115     | 0.135 |

| L   | 7.62 BSC    |       | 0.300 BSC |       |

| М   | —           | 10°   | _         | 10°   |

| N   | 0.76        | 1.01  | 0.030     | 0.040 |

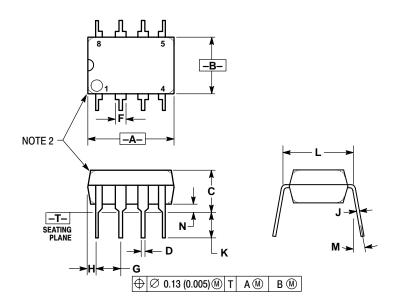

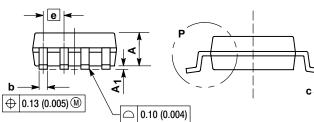

SO-8 **D SUFFIX** PLASTIC PACKAGE CASE 751-06 ISSUE T

- NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME

- DIMENSIONING AND TOLERANGING PERASME Y14.5M, 1994.

DIMENSIONS ARE IN MILLIMETER.

DIMENSION D AND E DO NOT INCLUDE MOLD PROTRUSION.

- 4 5.

PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 1.35        | 1.75 |  |  |

| A1  | 0.10        | 0.25 |  |  |

| В   | 0.35        | 0.49 |  |  |

| C   | 0.19        | 0.25 |  |  |

| D   | 4.80        | 5.00 |  |  |

| Е   | 3.80        | 4.00 |  |  |

| е   | 1.27 BSC    |      |  |  |

| н   | 5.80        | 6.20 |  |  |

| h   | 0.25        | 0.50 |  |  |

| L   | 0.40        | 1.25 |  |  |

| θ   | 0 °         | 7 °  |  |  |

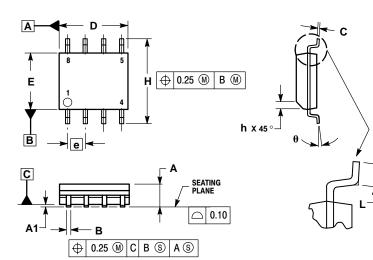

SOEIAJ-8 **M SUFFIX** PLASTIC PACKAGE CASE 968-01 ISSUE O

- NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER

DIMENSION D AND E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

THE LEAD WIDTH DIMENSION (b) DOES NOT INCLUDE DAMBAR PROTUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 (0.018). (0.018).

|                | MILLIMETERS |      | INCHES    |       |

|----------------|-------------|------|-----------|-------|

| DIM            | MIN         | MAX  | MIN       | MAX   |

| Α              |             | 2.05 |           | 0.081 |

| A1             | 0.05        | 0.20 | 0.002     | 0.008 |

| b              | 0.35        | 0.50 | 0.014     | 0.020 |

| C              | 0.18        | 0.27 | 0.007     | 0.011 |

| D              | 5.10        | 5.50 | 0.201     | 0.217 |

| E              | 5.10        | 5.45 | 0.201     | 0.215 |

| е              | 1.27 BSC    |      | 0.050 BSC |       |

| HE             | 7.40        | 8.20 | 0.291     | 0.323 |

| L              | 0.50        | 0.85 | 0.020     | 0.033 |

| LE             | 1.10        | 1.50 | 0.043     | 0.059 |

| М              | 0°          | 10°  | 0°        | 10°   |

| Q <sub>1</sub> | 0.70        | 0.90 | 0.028     | 0.035 |

| Ζ              |             | 0.94 |           | 0.037 |

## <u>Notes</u>

## <u>Notes</u>

**ON Semiconductor** and without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specification or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com Fax Response Line: 303–675–2167 or 800–344–3810 Toll Free USA/Canada

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor – European Support

- German Phone: (+1) 303–308–7140 (Mon–Fri 2:30pm to 7:00pm CET) Email: ONlit–german@hibbertco.com French Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET)

- French Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET) Email: ONlit-french@hibbertco.com

- English Phone: (+1) 303–308–7142 (Mon–Fri 12:00pm to 5:00pm GMT) Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781 \*Available from Germany, France, Italy, UK, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303–308–7143 (Mon–Fri 8:00am to 5:00pm MST) Email: ONlit–spanish@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support Phone: 303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time) Toll Free from Hong Kong & Singapore: 001–800–4422–3781 Email: ONlit–asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2745 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.